FPGA+DSP/ARM架構(gòu)開發(fā)與應(yīng)用

自中高端FPGA技術(shù)成熟以來(lái),F(xiàn)PGA+DSP/ARM架構(gòu)的硬件設(shè)計(jì)在眾多工業(yè)領(lǐng)域得到廣泛應(yīng)用。例如....

Pico2-ICE FPGA開發(fā)板的應(yīng)用示例

FPGA 和 MCU 結(jié)合的開發(fā)板不多,而 Pico2?ICE 則把小巧、靈活和易上手完美結(jié)合。搭載....

雷達(dá)系統(tǒng)中數(shù)字下變頻的實(shí)現(xiàn)

本次設(shè)計(jì)同樣是通過(guò)在simulink搭建模型并通過(guò)matlab仿真得到正確設(shè)計(jì)后生成IP核的形式來(lái)實(shí)....

vivado仿真時(shí)GSR信號(hào)的影響

利用vivado進(jìn)行設(shè)計(jì)xilinx FPGA時(shí),寫完設(shè)計(jì)代碼和仿真代碼后,點(diǎn)擊run simula....

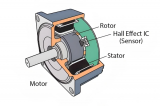

使用Verilog在FPGA上實(shí)現(xiàn)FOC電機(jī)控制系統(tǒng)

在自動(dòng)駕駛、電動(dòng)滑板車、無(wú)人機(jī)甚至工業(yè)自動(dòng)化領(lǐng)域,高性能電機(jī)控制是不可或缺的核心技術(shù)。而如果你對(duì)硬件....

基于FPGA和USB3.0通信的UVC攝像機(jī)設(shè)計(jì)方案

本次演示用的是USB3.0芯片-CYPRESS CYUSB3014(下稱 FX3),該芯片是標(biāo)準(zhǔn)的U....

基于FPGA的數(shù)字識(shí)別系統(tǒng)設(shè)計(jì)

在圖像處理領(lǐng)域,圖像識(shí)別是較為困難而關(guān)鍵的技術(shù)。這項(xiàng)技術(shù)被廣泛的應(yīng)用到娛樂、工業(yè)、軍事等領(lǐng)域。本次設(shè)....

基于FPGA YOLO算法的掃描式SMT焊點(diǎn)缺陷檢測(cè)系統(tǒng)設(shè)計(jì)

作為電子產(chǎn)品最重要的組成部分,印刷電路板(PCB)的設(shè)計(jì)日趨復(fù)雜和器件尺寸的縮小,促使對(duì) SMT 可....

基于Matlab與FPGA的雙邊濾波算法實(shí)現(xiàn)

前面發(fā)過(guò)中值、均值、高斯濾波的文章,這些只考慮了位置,并沒有考慮相似度。那么雙邊濾波來(lái)了,既考慮了位....

基于FPGA LMS算法的自適應(yīng)濾波器設(shè)計(jì)

自適應(yīng)濾波是近幾十年發(fā)展起來(lái)的信號(hào)處理理論的的新分支。隨著人們?cè)谠擃I(lǐng)域研究的不斷深入,自適應(yīng)處理的理....

基于FPGA的SSD目標(biāo)檢測(cè)算法設(shè)計(jì)

隨著人工智能的發(fā)展,神經(jīng)網(wǎng)絡(luò)正被逐步應(yīng)用于智能安防、自動(dòng)駕駛、醫(yī)療等各行各業(yè)。目標(biāo)識(shí)別作為人工智能的....

基于FPGA的壓縮算法設(shè)計(jì)

本設(shè)計(jì)中,計(jì)劃實(shí)現(xiàn)對(duì)文件的壓縮及解壓,同時(shí)優(yōu)化壓縮中所涉及的信號(hào)處理和計(jì)算密集型功能,實(shí)現(xiàn)對(duì)其的加速....

一種集成FPGA和DSP芯粒的異構(gòu)系統(tǒng)級(jí)封裝

將多個(gè)異構(gòu)芯粒集成在一起進(jìn)行封裝是一種具有廣闊前景且成本效益高的策略,它能夠構(gòu)建出既靈活又可擴(kuò)展的系....

FPGA遠(yuǎn)程燒寫bit文件和調(diào)試ILA指南

在 FPGA 開發(fā)過(guò)程中,燒寫bit文件和使用ILA進(jìn)行調(diào)試是再常見不過(guò)的操作。但如果 FPGA 板....

詳解Xilinx的10G PCS PMA IP

如果要在Xilinx的FPGA上使用萬(wàn)兆以太網(wǎng)通信,大致有三種方法構(gòu)建協(xié)議棧。第一種使用GTX等Se....

FPGA Verilog HDL語(yǔ)法之編譯預(yù)處理

Verilog HDL語(yǔ)言和C語(yǔ)言一樣也提供了編譯預(yù)處理的功能?!熬幾g預(yù)處理”是Verilog HD....

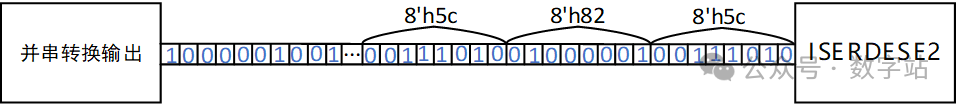

ISERDESE2原語(yǔ)端口及參數(shù)介紹

前面在講解HDMI接口之前,講解過(guò)IDDR、ODDR、OSERDESE2、IBUF等原語(yǔ),之后一直有....

FPGA標(biāo)準(zhǔn)庫(kù)Open Logic介紹

在現(xiàn)代技術(shù)發(fā)展的浪潮中,開源項(xiàng)目已經(jīng)成為了推動(dòng)技術(shù)創(chuàng)新和發(fā)展的核心力量。無(wú)論是人工智能、區(qū)塊鏈、云計(jì)....

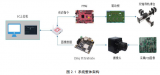

如何通過(guò)串口將8路adc采集的數(shù)據(jù)傳輸給上位機(jī)顯示

01 概括 ? 前文提供了ad7606的驅(qū)動(dòng)程序,本文通過(guò)串口將8路adc采集的數(shù)據(jù)傳輸給上位機(jī)顯示....

基于FPGA的FIR數(shù)字濾波器設(shè)計(jì)

在現(xiàn)代通信信號(hào)處理領(lǐng)域中,隨著各種精密計(jì)算和快速計(jì)算的發(fā)展對(duì)信號(hào)處理的實(shí)時(shí)性、快速性的要求越來(lái)越高。....

DeepSeek接入到VSCode實(shí)現(xiàn)提詞及代碼助寫

在AI大火之后,AI代碼一直是討論的熱題,之前比較火的cursor就是基于此出現(xiàn)的,但是國(guó)內(nèi)訪問(wèn)受限....

使用DDS生成三個(gè)信號(hào)并在Vivado中實(shí)現(xiàn)低通濾波器

本文使用 DDS 生成三個(gè)信號(hào),并在 Vivado 中實(shí)現(xiàn)低通濾波器。低通濾波器將濾除相關(guān)信號(hào)。

三維空間降噪裝置設(shè)計(jì)方案

隨著現(xiàn)代工業(yè)化進(jìn)程的加快,噪聲污染已上升為一個(gè)嚴(yán)重的環(huán)境問(wèn)題,和水污染、空氣污染、固體廢棄物污染一起....

基于FPGA的圖像邊緣檢測(cè)設(shè)計(jì)

今天給大俠帶來(lái)基于 FPGA 的圖像邊緣檢測(cè)設(shè)計(jì),話不多說(shuō),上貨。 設(shè)計(jì)流程如下:mif文件的制作→....

DeepSeek在FPGA/IC領(lǐng)域的創(chuàng)新應(yīng)用及未來(lái)展望

隨著人工智能技術(shù)的飛速發(fā)展,以DeepSeek為代表的大語(yǔ)言模型(LLM)正在逐步滲透到傳統(tǒng)硬件開發(fā)....

Intel為什么在2015年收購(gòu)Altera?現(xiàn)在又為什么拋棄Altera

在寫這篇文章時(shí),我想了很多標(biāo)題,但總感覺沒有哪個(gè)能把文章的意思全都總結(jié)清楚的,所以我又起了副標(biāo)題:斷....