三維集成電路與晶圓級(jí)3D集成介紹

微電子技術(shù)的演進(jìn)始終圍繞微型化、高效性、集成度與低成本四大核心驅(qū)動(dòng)力展開(kāi),封裝技術(shù)亦隨之從傳統(tǒng)TSO....

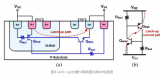

CMOS集成電路中閂鎖效應(yīng)的產(chǎn)生與防護(hù)

閂鎖效應(yīng)(Latch-up)是CMOS集成電路中一種危險(xiǎn)的寄生效應(yīng),可能導(dǎo)致芯片瞬間失效甚至永久燒毀....

淺談三維集成封裝技術(shù)的演進(jìn)

在半導(dǎo)體封裝領(lǐng)域,堆疊技術(shù)作為推動(dòng)高集成度與小型化的核心趨勢(shì),正通過(guò)垂直堆疊芯片或封裝實(shí)現(xiàn)更緊湊的封....

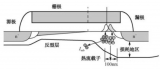

熱載流子注入效應(yīng)對(duì)芯片有什么危害

熱載流子注入效應(yīng)(Hot Carrier Inject, HCI)是半導(dǎo)體器件(如晶體管)工作時(shí),高....

功率半導(dǎo)體晶圓級(jí)封裝的發(fā)展趨勢(shì)

在功率半導(dǎo)體封裝領(lǐng)域,晶圓級(jí)芯片規(guī)模封裝技術(shù)正引領(lǐng)著分立功率器件向更高集成度、更低損耗及更優(yōu)熱性能方....

3D封裝架構(gòu)的分類(lèi)和定義

3D封裝架構(gòu)主要分為芯片對(duì)芯片集成、封裝對(duì)封裝集成和異構(gòu)集成三大類(lèi),分別采用TSV、TCB和混合鍵合....

淺談SPICE模型參數(shù)自動(dòng)化提取

在過(guò)去的幾十年里,半導(dǎo)體器件緊湊型模型已經(jīng)從 BJT Gummel-Poon 模型中的幾個(gè)參數(shù)發(fā)展到....

詳解芯片制造中的可測(cè)性設(shè)計(jì)

然而,隨著納米技術(shù)的出現(xiàn),芯片制造過(guò)程越來(lái)越復(fù)雜,晶體管密度增加,導(dǎo)致導(dǎo)線短路或斷路的概率增大,芯片....

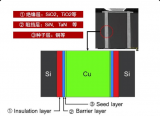

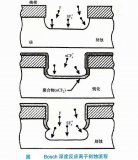

硅通孔電鍍材料在先進(jìn)封裝中的應(yīng)用

硅通孔(TSV)技術(shù)借助硅晶圓內(nèi)部的垂直金屬通孔,達(dá)成芯片間的直接電互連。相較于傳統(tǒng)引線鍵合等互連方....

系統(tǒng)級(jí)立體封裝技術(shù)的發(fā)展與應(yīng)用

系統(tǒng)級(jí)立體封裝技術(shù)作為后摩爾時(shí)代集成電路產(chǎn)業(yè)的核心突破方向,正以三維集成理念重構(gòu)電子系統(tǒng)的構(gòu)建邏輯。

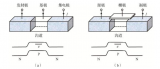

晶體管的基本結(jié)構(gòu)和發(fā)展歷程

隨著集成電路科學(xué)與工程的持續(xù)發(fā)展,當(dāng)前集成電路已涵蓋二極管、晶體管、非易失性存儲(chǔ)器件、功率器件、光子....

集成電路制造中封裝失效的機(jī)理和分類(lèi)

隨著封裝技術(shù)向小型化、薄型化、輕量化演進(jìn),封裝缺陷對(duì)可靠性的影響愈發(fā)凸顯,為提升封裝質(zhì)量需深入探究失....

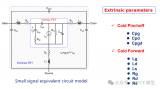

集成電路中場(chǎng)效應(yīng)晶體管的寄生參數(shù)提取方法

柵極電阻的存在對(duì)電路性能的影響很大,會(huì)引入熱噪聲,增大電路的噪聲系數(shù),影響器件的開(kāi)關(guān)速度和最大振蕩頻....

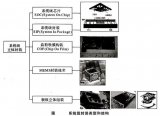

HBM技術(shù)在CowoS封裝中的應(yīng)用

HBM通過(guò)使用3D堆疊技術(shù),將多個(gè)DRAM(動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)芯片堆疊在一起,并通過(guò)硅通孔(TSV....

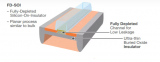

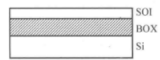

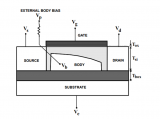

一文詳解BSIM-SOI模型

隨著半導(dǎo)體工藝進(jìn)入納米尺度,傳統(tǒng)體硅(Bulk CMOS)技術(shù)面臨寄生電容大、閂鎖效應(yīng)等瓶頸。SOI....

拉曼光譜的基礎(chǔ)知識(shí)

想象一下,如果我們能夠"聽(tīng)見(jiàn)"分子的"聲音",那會(huì)是什么樣的?拉曼光譜技術(shù)正是這樣一種神奇的工具,它....

電源管理芯片常見(jiàn)術(shù)語(yǔ)

PMIC (Power Management Integrated Circuit):電源管理集成電....

一文詳解TEM中的非彈性散射和電子束損傷

為什么非彈性散射值得我們關(guān)注?因?yàn)檫@類(lèi)散射過(guò)程產(chǎn)生了多種信號(hào),每種信號(hào)都能提供比彈性電子更豐富的樣品....

離子注入技術(shù)的常見(jiàn)問(wèn)題

離子注入單晶靶材時(shí),因靶體存在特定晶向,其對(duì)入射離子的阻滯作用不再如非晶材料般呈現(xiàn)各向同性。沿硅晶體....

一文詳解TEM中的彈性散射

彈性散射電子是TEM圖像襯度的主要來(lái)源,同時(shí)也產(chǎn)生衍射圖樣(DPs)的大部分強(qiáng)度,因此理解控制這一過(guò)....